## HEWLETT: APPLICATION NOTE 944-1

# **Microwave Transistor Bias Considerations**

#### INTRODUCTION

Often the least considered factor in microwave transistor circuit design is the bias network. Considerable effort is spent in measuring s-parameters, calculating gain, and optimizing bandwidth and noise figure, while the same resistor topology is used to bias the transistor. Since the cost per dB of microwave gain or noise figure is so high, the circuit designer cannot afford to sacrifice RF performance by inattention to dc bias considerations.

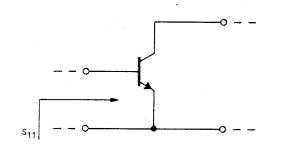

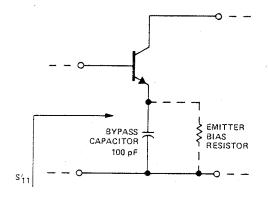

Microwave transistor amplifier design requires biasing the transistor into the active region of performance and holding this bias or quiescent point constant over variations in temperature. At low frequencies, emitter resistor stabilization with negative current feedback is used for dc stability. At microwave frequencies the bypass capacitor becomes a problem since a good RF bypass at the design frequency often introduces low frequency instability and gives rise to bias oscillations. Figure 1 shows this effect.

In low noise amplifier applications, even if a capacitor could be chosen to provide effective RF and low frequency emitter bypass, any small series emitter impedance at the operating frequency would reflect in a large noise figure degradation. Most microwave circuit designs for best gain or lowest noise figure will require that the emitter lead be dc grounded as close to the package as possible so that the emitter series feedback is kept at an absolute minimum,

It has been found\* that the principle dependent variable in dc stability analysis is the collector current (Ic). The transistor parameters that are temperature sensitive and influence Ic are examined along with some passive resistive circuits that give stable dc operation and allow for trimming due to variations in transistor types.

S<sub>11</sub> (at 4 GHz) = .52 ∠154°  $S_{11}$  (at .1 GHz) = .901  $\angle$  -14.9°

s-parameters of grounded emitter transistor at 4 GHz and .1 GHz.

$S'_{11}$  (at 4 GHz) = .52  $\angle$  154° unchanged at 4 GHz  $S'_{11}(at..1 \text{ GHz}) = 1.066 \angle -8.5^{\circ} |S_{11}| > 1 \text{ at .1 GHz}$

s-parameters, of same transistor with good 4 GHz emitter bypass capacitor. S'11 at 4 GHz remains unchanged while |S11| at .1 GHz is greater than 1 indicating conditional stability.

In order to best select an optimum bias network, a method of comparison has to be developed. Analysis of transistor bias network instability involves writing a collector current equation in terms of the transistor equivalent circuit and the external bias circuitry. Partial derivatives of the collector current, with respect to the temperature dependent variables, are calculated individually and the resultant stability factors can then be considered simultaneously to predict collector current temperature behavior.

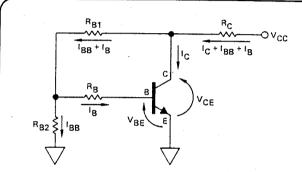

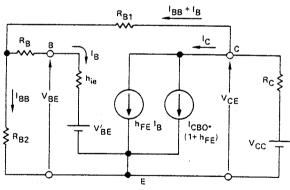

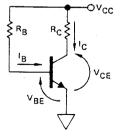

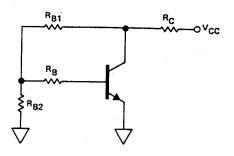

A look at the typical bias circuit of Figure 2a and its dc equivalent circuit in Figure 2b identifies the internal parameters that affect collector current. Since the external resistors have negligible temperature change compared to the transistor, the temperature sensitive parameters are found to be  $V_{\text{ME}}$ ,  $I_{\text{CBO}}$ , and  $h_{\text{FE}}$ .

A. Bias circuit showing only the DC components.

B. The equivalent circuit of Figure 2a is used in DC stability analysis.

NOTES: V'BE is internal to the transistor and has a  $-2mV/^{\circ}C$  temperature coefficient.

$h_{ie}$  is the hybrid- $\pi$  input impedance and for Hewlett-Packard microwave transistors is approximately 500 ohms. The exact value is unimportant since  $h_{ie}$  is always in series with the larger base bias resistor Rg. It is only included for completeness.

#### ■ Base Emitter Voltage (V<sub>BF</sub>)

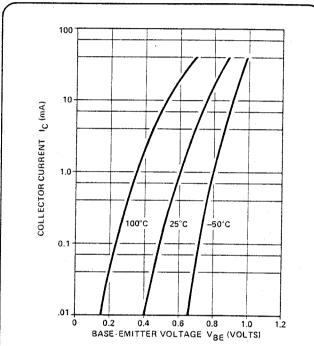

$V_{\text{BE}}$  is the base-emitter voltage.  $V_{\text{BE}}$  is internal to the transistor and has a negative temperature coefficient of -2 mV/°C. Figure 3a shows a typical silicon PN junction current-voltage relation. Notice the negative shift in threshold voltage for increased temperatures. A bias circuit that fixes a constant voltage on the base, independent of temperature, will find the collector current increasing for increasing temperature. Fortunately, negative voltage feedback will help compensate for  $V_{\text{BE}}$  changes as illustrated in Figure 3b and 3c.

A. Typical base-emitter voltage (VBE) vs. collector current (C) curve showing the threshold shift due to sensitivity of V'BE = -2 mV/°C.

B. Bias Network that uses no feedback and is sensitive to changes in V'BE, ICBO, and hee.

C. Bias network that uses voltage feedback and is less sensitive to changes in V'BE, ICBO, and hee.

Figure 2.

#### ■ Reverse Collector Current (I<sub>CBO</sub>)

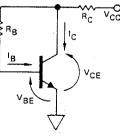

$I_{\text{CBO}}$  is the current flowing through a reverse biased PN junction. Classically, this leakage current is expected to double for every 10°C temperature rise in a silicon semiconductor junction.

Microwave transistors have a more complicated reverse current flow. A small component of this current flow is a conventional  $I_{\text{C8O}}$  term but the major contributor is a surface current that flows across the top of the silicon crystal lattice and this surface current is a more linear function of temperature than the  $I_{\text{C8O}}$  current. The total reverse current, made up of  $I_{\text{C8O}}$  and surface components, increases at a rate much less than that which would be expected from an  $I_{\text{C8O}}$  current alone of the same magnitude. A typical reverse current versus temperature relationship is shown for several HP microwave transistors in Figure 4. The data applies to a collector-base voltage of 10 volts.

Figure 4.

In general, the slope of the  $I_{CBO}$  curve for HP microwave transistors remains unchanged with reverse bias. For stability calculations a family of curves, at specified collector to base voltages, can be considered to follow the slope of the curve with intercepts at 25°C corresponding to the data sheet or measured value of  $I_{CBO}$ .

#### ■ DC Current Gain (h<sub>FE</sub>)

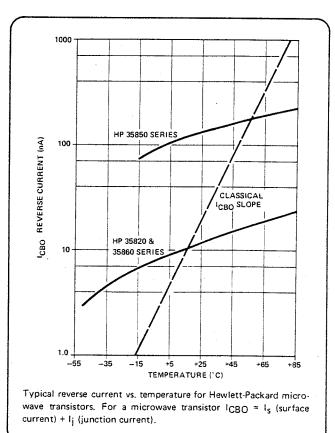

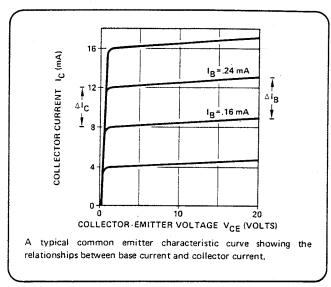

The typical characteristic curve of Figure 5 shows the collector current versus collector to emitter voltage for a constant base current.

The  $h_{\text{fe}}$  is defined as the ratio of the change of collector current to the change in base current

$$h_{fe} = \beta = \Delta I_{C} \over \Delta I_{B} \mid V_{CE} = constant$$

Figure 5.

$h_{FE}$ , the dc value of the current gain, is defined as the ratio of the collector current ( $I_C$ ) to base current ( $I_R$ ).

$$h_{FE} = \beta_{DC} = \frac{I_C}{I_B} \Big|_{V_{CE}} = constant$$

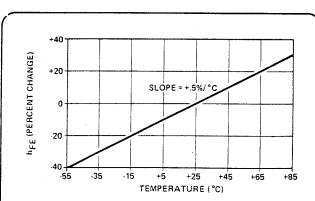

It is this dc value of  $h_{FE}$  that is used in the stability calculations and it is found to typically increase linearly with temperature at the rate of 0.5% /°C. Figure 6 shows the temperature dependence of  $h_{FF}$ .

Typical percent change in hFE versus temperature (normalized to  $25^{\circ}$ C).

Figure 6.

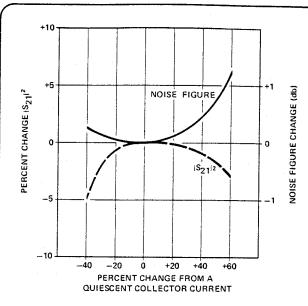

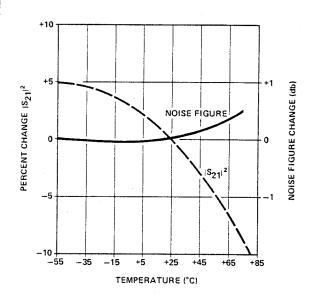

A look at the four s-parameters and noise figure of HP microwave transistors reveals that  $|S_{21}|^2$  and noise figure stand out as the most sensitive parameters to small changes in bias. Also, both of these parameters are stronger functions of collector current (I<sub>C</sub>) than of collector to emitter voltage (V<sub>CE</sub>). This means that if we know something about how  $|S_{21}|^2$  and noise figure change with collector current and with temperature, then some constraints can be placed on the bias network to minimize changes in RF performance over a specified temperature range.

The typical data shown in Figure 7a is normalized to percentage changes in both gain and collector current. The noise figure change is plotted in dB. Although the absolute gain and noise figure are frequency dependent, their sensitivity with respect to collector current ( $I_{\rm C}$ ) can be considered frequency independent. Notice that a 20% increase in collector current has a very small effect on either a transistor biased for minimum noise figure or a transistor biased for maximum gain.

Next, a look at some typical changes in noise figure and gain as a function of temperature (Figure 7b) shows that both NF and gain degrade with increasing temperature. We see, for example, that a bias network that can hold the quiescent point such that the current does not increase more than 20% to 60°C will have a 5% degradation in gain or a 0.3 dB increase in noise figure at 60°C due to transistor changes alone. Some temperature compensation could be designed into the bias circuitry by using lower values of collector current at 25°C and allowing the temperature sensitivity of the bias network to offset the temperature sensitivity of the transistor.

It should be pointed out that each amplifier function has a different bias requirement. In other words, transistors used in gain stages in which the noise figure or the saturated output power are not critical have a much more relaxed bias stability requirement than, say, a low noise front-end transistor. This can be seen in Figure 7a since  $|S_{21}|^2$  has a broad maximum compared to noise figure. A transistor biased for high linear output power must hold its quiescent point such that the 1 dB compression point is not degraded with temperature and so that the maximum power dissipation in the device is not exceeded with increasing temperature.

A. Typical change in performance as a function of collector current variation for a transistor biased at minimum noise figure and a transistor biased at maximum gain.

B. Typical change in performance as a function of temperature variation for a transistor biased at minimum noise figure and a transistor biased at maximum gain (normalized to 25°C).

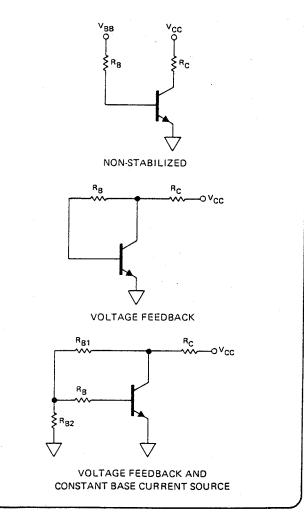

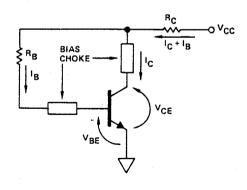

#### SUGGESTED BIAS CIRCUITS

Three bias circuit topologies are shown in Table 1 along with a general expression for the collector current and the calculated dc bias stability factors for  $V_{\rm EB}'$ ,  $I_{\rm CBO}$  and  $h_{\rm FE}$ . Most microwave circuit designs, for reasons of noise figure, gain, and RF stability will require a dc grounded emitter; therefore, emitter resistor stabilized circuits will not be considered. The grounded emitter non-stabilized bias circuit (Table 1a) finds very little usage in microwave circuit design since it exhibits the least dc bias stability.

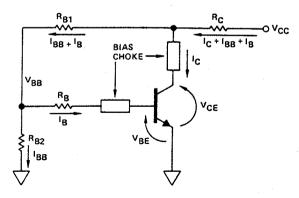

Both circuits in Tables 1b and 1c find widespread usage as bias networks. The voltage feedback circuit uses fewer components and is almost as temperature stable as Table 1c. The addition of  $R_{\rm B1}$  and  $R_{\rm B2}$  to the voltage feedback circuit does two things. First, it makes all the element values lower in resistance and this makes it more compatible with thin/thick film resistor values. In the voltage feedback circuit the value of Ra would typically be in the range of 30 k $\Omega$  to 100 k $\Omega$  and these values are difficult to achieve in hybrid integrated circuits. Second, the circuit of 1c can be considered to have a constant base current source, through Rs, and this then allows for trimming, on a production basis, to initially set the collector current to the desired value. The collector current cannot be measured directly since the current in R<sub>c</sub> is made up of base current, base bias network current, and collector current. However, since  $I_c$  is proportional to  $V_{CE}$ , monitoring  $V_{CE}$ while adjusting R<sub>8</sub> accommodates any value of her that will be encountered in HP transistors.

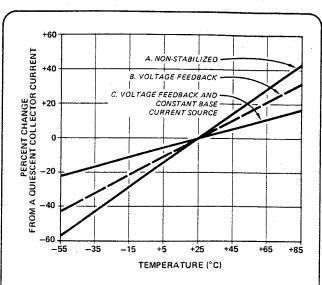

Differences in collector current stability for each topology are compared in Figure 8. It is important to point out that, for the sake of comparison, each circuit was used to bias the transistor to a common quiescent point. This data is typical for frequently encountered microwave bias circuits and is valuable in relative comparisons. Notice that for each of the circuits, the collector current is a positive linear function of temperature. And from Figure 7a, we see that noise figure degradation and gain are negative functions of both collector current and junction temperature.

#### BIBLIOGRAPHY

- "Electronic Circuit Analysis" Philip Cutler. Volume

McGraw-Hill 1967. Chapters 4-11, pages 220-228.

- "Analysis and Design of Electronic Circuits" P. M. Chirlian. McGraw-Hill. Chapters 2, 4, pages 58-61.

- "G.E. Transistor Manual" Sixth Edition 1962. Chapter 7, pages 101-109.

- "Transistor Circuit Analysis" Maurice V. Joyce and Kenneth K. Clark. Addison-Wesley 1961. Pages 66-81.

- "Transistor Circuit Analysis and Design" John J. Corning. Prentice-Hall 1965. Pages 91-115.

Typical DC stability performance of each bias network (Table 1) used to bias Hewlett-Packard microwave transistors. Graph shows the percent change from a nominal quiescent collector current as a function of temperature (normalized to 25°C).

Figure 8.

#### **Table 1. Microwave Transistor Stability Factors**

Bias networks for DC grounded emitter operation. For each circuit the general expression for the collector current along with the stability factors are given.

The "voltage feedback" circuit of 1B and the "voltage feedback and constant base current" circuit of 1C will provide for temperature stable DC operation and complement the RF Performance of the following Hewlett-Packard transistor series:

HP 35820, HP 35850, HP 35860.

The non-stabilized circuit of 1A is not recommended and is only shown for comparison.

$$\frac{h_{FE} (V_{BB} - V'_{BE})}{(h_{ie} + R_B)} + I_{CBO} (1 + h_{FE})$$

ICBO STABILITY FACTOR

$$\partial I_{CBO} = \frac{\partial IC}{\partial I_{CBO}} \bigg|_{h \in E, V'_{BE} = constant}$$

V'BE STABILITY FACTOR

$$\partial V'BE = \frac{\partial IC}{\partial V'BE}$$

hFE, ICBO = constant

HE STABILITY FACTOR

$$\partial h_{FE} = \frac{\partial I_{C}}{\partial h_{FE}} \bigg|_{h_{FE}, V'_{BE} = constant}$$

\_ USE OF STABILITY FACTORS \_

$$S_{I_{CBO}} = \frac{\partial I_{CBO}}{\partial I_{CBO}} \Big|_{h \in E, V'_{BE}} = Constant$$

$$S_{V'BE} = \frac{\partial I_C}{\partial V'BE} \bigg|_{ICBO, hFE} = Constant$$

$$S_{h_{FE}} = \frac{\partial I_C}{\partial h_{FE}} \Big|_{I_{CBO}, V'_{BE}} = Constant$$

$$\Delta_{IC} = \frac{9IC}{9ICBO} \cdot \Delta_{ICBO} + \frac{9AC}{9IC} \cdot \Delta_{ACBE} \cdot \Delta_{ACBE} + \frac{9IC}{9IC} \cdot \Delta_{BE} + \frac{9IC}{9IC}$$

First calculate the stability factors for  $V'_{BE}$ ,  $I_{CBO}$ , and  $h_{FE}$ . Then, to find the change in collector current at any temperature, multiply the change from 25°C of each temperature dependent variable with its corresponding stability factor and sum.

It would appear to be an easy task to further analyze the individual stability factors for minimums in terms of the external circuit resistor values. This is not too easily done since all the factors are inter-related. The stability factors must be considered simultaneously since an optimum set of resistor values to minimize one parameter could grossly increase another.

C. VOLTAGE FEEDBACK AND CONSTANT BASE CURRENT SOURCE

$$\frac{h_{FE} (^{V}CC - ^{V}BE)^{l+1}CBO (1 + h_{FE}) (h_{ie} + ^{R}B^{+R}C)}{h_{ie} + ^{R}B + ^{R}C (1 + h_{FE})} \qquad h_{FE} \left\{ \frac{-V_{BE} A - R_{B2}[(R_{C} | CBO (1 + h_{FE}) - VCC)]}{(R_{B} + h_{ie}) A + ^{R}B_{2} (h_{FE} R_{C} + R_{C} + R_{B1})} \right\} + I_{CBO} (1 + h_{FE})$$

$$\frac{(1 + h_{FE}) (h_{ie} + R_{B} + R_{C})}{h_{ie} + R_{B} + R_{C} (1 + h_{FE})} \qquad (1 + h_{FE}) - \left( \frac{R_{B2} H_{FE} R_{C} (1 + h_{FE})}{A (R_{B} + h_{ie}) + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})} \right)$$

$$\frac{-h_{FE}}{h_{ie} + R_{B} + R_{C} (1 + h_{FE})} \qquad \frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE}}{h_{ie} + R_{B} + R_{C} (1 + h_{FE})} \qquad \frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie}) A + R_{B2} (h_{FE} R_{C} + R_{C} + R_{B1})}$$

$$\frac{-h_{FE} A}{(R_{B} + h_{ie})$$

### **DESIGN EXAMPLES**

Some examples of how to go about calculating the resistor values for the two most commonly used grounded emitter bias circuits are given below. The resistor values are calculated and the nearest standard 1% tolerance resistor values are shown. Depending upon the exact application, other tolerance resistors can be used with little or no difference. Also

listed in tabular form, are other resistor values that have been calculated for the indicated quiescent points at a 20 volt supply voltage. Other supply voltages can be calculated accordingly.

For bias circuit designs with HP microwave transistors, assume h<sub>fé</sub> = 50 and neglect his

#### EXAMPLE 1

- Determine supply voltage available (VCC = 20V) and transistor operating bias point (10V, 10mA), assume ICBO = 0, VBE = .7 volts.

- Knowing the measured value of hfe, (or assume 50), calculate base current IB (mA) = IC (mA)/hfe = 10/50 = .2 mA.

- 3. Calculate RB knowing VBE = .7V and VCE = 10V

$$R_{B} (K\Omega) = \frac{V_{C} - V_{BE}}{I_{B}} = \frac{(Volts)}{(mA)} = \frac{10 - .7}{.2} = 46.5 K\Omega$$

(use R<sub>B</sub> = 46.4 KΩ

4. Calculate Rc

$$R_{C}(K\Omega) = \frac{V_{CC} - VC}{I_{C} + I_{B}} = \frac{(Volts)}{(mA)} = \frac{20 - 10}{10 + .2} = .98K\Omega$$

(use  $R_{C} = 1 K\Omega$ )

Note that a  $\pm$  20% error in assuming a value of hFE will only change  $1c \pm 1$  mA.

- The general equation for collector current can now be used to check the design using actual calculated resistor values.

- 6. After the transistor circuit is constructed a quick measurement of VCE will ensure that the device is biased correctly. Since VCE is proportional to 1/hFE, the base resistor (RB) can be adjusted accordingly to compensate for manufacturing variations in hFE. This is easily done by varying RB while monitoring VCE to properly obtain the desired collector current.

## TABLE OF TYPICAL RESISTOR VALUES FOR INDICATED BIAS (V<sub>CC</sub> = 20V)

| BIAS      | pEE | RB     | RC     |  |

|-----------|-----|--------|--------|--|

| 10V, 5mA  | 50  | 90.9ΚΩ | 1.96ΚΩ |  |

| 10V, 10mA | 50  | 46.4KΩ | 1ΚΩ    |  |

| 15V, 15mA | 50  | 46.4ΚΩ | 348Ω   |  |

|           |     |        |        |  |

#### **EXAMPLE 2**

- Determine supply voltage available (V<sub>CC</sub> = 20V) and transistor bias operating point (10V, 10mA). Assume I<sub>CBO</sub> = 0, V<sub>BE</sub> = .7V.

- 2. Select VBB to be 2V to ensure constant base current source.

- Knowing the measured value of hfe, (or assume 50), calculate base current ig (mA) - ic (mA)/hfe = 10/50 = .2 mA.

- 4. Calculate Rg knowing VBE = .7V and VBB = 2V

$$R_{B} (K\Omega) = \frac{V_{BB} - V_{BE}}{I_{B}} = \frac{(Volts)}{(mA)} = \frac{2 - .7}{.2} = 6.5 K\Omega$$

(use R<sub>B</sub> = 6.81K)

Calculate RB2 assuming IBB = 1 mA

$$R_{B2} (K\Omega) = \frac{V_{BB}}{I_{BB}} = \frac{(Volts)}{(mA)} = \frac{2}{1} = 2K\Omega$$

(use R<sub>B2</sub> = 1.96K)

6. Now calculate Rg1 knowing Ig, Igg, Vgg and Vcc

$$R_{B1} (K\Omega) = \frac{V_{CE} - V_{BB}}{I_{BB} + I_{B}} = \frac{(Volts)}{(mA)} = \frac{10 - 2}{1.2} = 6.66 K\Omega$$

(use  $R_{B1} = 6.19 K$ )

7. Calculate RC knowing IC, IBB + IB, VCC and VCE

$$R_C(K\Omega) = \frac{V_{CC} - V_{CE}}{I_C + I_{BB} + I_B} = \frac{(Volts)}{(mA)} = \frac{20 - 10}{10 + 1.2} = .893K\Omega$$

(use  $R_C = 909\Omega$ )

- The general equation for collector current can now be used to check the design using actual calculated resistor values.

- After the circuit is designed, R<sub>B</sub> may be adjusted to obtain an exact value of I<sub>C</sub>.

### TABLE OF TYPICAL RESISTOR VALUES FOR INDICATED BIAS (V<sub>CC</sub> = 20V)

|           |     | <b>99</b>    |                   |                   |                   |  |  |  |

|-----------|-----|--------------|-------------------|-------------------|-------------------|--|--|--|

| BIAS      | pEE | RC           | RB                | R <sub>B1</sub>   | R <sub>B2</sub>   |  |  |  |

| 10V, 5mA  | 50  | 1.62ΚΩ       | 12.1ΚΩ            | 7.5ΚΩ             | 1.96ΚΩ            |  |  |  |

| 10V, 10mA | 50  | $\Omega$ e0e | 6.81KΩ            | $6.19$ K $\Omega$ | $1.96$ K $\Omega$ |  |  |  |

| 15V, 15mA | 50  | 316Ω         | $4.22$ K $\Omega$ | 10ΚΩ              | $1.96$ K $\Omega$ |  |  |  |

|           |     |              |                   |                   |                   |  |  |  |

Hewlett Packard assumes no responsibility for the use of any circuits described herein and makes no representations or warranties, express or implied, that such circuits are free from patent infringement.

For more information call your local HP Sales Office or East (301) 948-6370 — Midwest (312) 255-9800 — South (404) 955-1500 — West (213) 970-7500. Or write: Hewlett-Packard Components, 350 West Trimble Road. San Jose, California 95131. In Europe, Hewlett-Packard GmbH. P.O. Box 250, Herrenberger Str. 110, 0-7030 Boeblingen, West Germany. In Japan. YHP, 3-29-21, Takaido-Higashi, Suginami Ku, Tokyo 168